# ISL6140/41EVAL1 Board

Application Note

June 2002

AN1020

#### ISL6140/41Negative Voltage Hot Plug Controller

The ISL6140 is an 8-pin, negative voltage hot plug controller that allows a board to be safely inserted and removed from a live backplane. Inrush current is limited to a programmable value by controlling the gate voltage of an external Nchannel pass transistor. The pass transistor is turned off if the input voltage is less than the Under-Voltage threshold, or greater than the Over-Voltage threshold. A programmable electronic circuit breaker protects the system against shorts. The active low PWRGD signal can be used to directly enable a power module (with a low enable input). The ISL6150 is the same part, but with an active high PWRGD signal.

The ISL6141/51 are pin compatible with the ISL6140/50. In addition to the features noted above these enhanced hot plug controllers offer programmable current limiting with a 600us time-out. When the Over-Current threshold is exceeded, the output current is limited for 600us before the circuit breaker shuts down the FET. If the fault disappears before the 600µs time-out, normal operation resumes. The new IntelliTrip<sup>™</sup> electronic circuit breaker has a fast Hard Fault shutdown with a threshold set at 4 times the current limit value. When activated, the GATE is immediately turned off and then slowly turned back on for a single retry (softstart). The GATE and DRAIN voltages are both monitored with separate comparators to enable the Power Good output at start-up. When the DRAIN and GATE voltage conditions are met, the comparators trip and latch the PWRGD/PWRGD output into the active state. At this point

any of the signals that turn off the gate will reset the latch and drive the PWRGD/PWRGD output inactive.

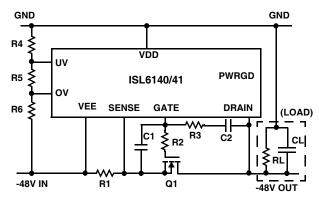

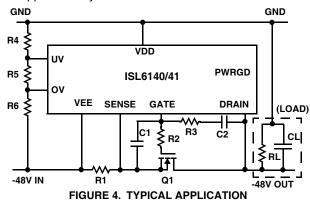

# **Typical Application**

R1 =  $0.02\Omega$  (1%) R2 =  $10\Omega$  (5%) R3 =  $18k\Omega$  (5%) R4 =  $549k\Omega$  (1%) R5 =  $6.49k\Omega$  (1%) R6 =  $10k\Omega$  (1%)  $\begin{array}{l} \text{C1} = 150 \text{nF} \ (25 \text{V}) \\ \text{C2} = 3.3 \text{nF} \ (100 \text{V}) \\ \text{Q1} = \text{IRF530} \ (100 \text{V}, \ 17 \text{A}, \ 0.11 \Omega) \\ \text{CL} = 100 \mu \text{F} \ (100 \text{V}) \\ \text{RL} = \text{equivalent load} \end{array}$

- Features (ISL6140/41/50/51)

- Low Side External NFET Switch

- ISL6140/50 operates from -10V to -80V (-100V absolute max rating) or +10V to +80V (+100V absolute max rating)

- ISL6141/51operates from -20V to -80V (-100V absolute max rating) or +20V to +80V (+100V absolute max rating)

- Programmable Inrush Current

- Programmable Electronic Circuit Breaker (Over-Current shutdown)

- Programmable Over-Voltage Protection

- Programmable Under-Voltage Protection

- Power Good Control Output

- PWRGD Active High: (H Version) ISL6150/51

- PWRGD Active Low: (L Version) ISL6140/41

# Features (ISL6141/51)

- Programmable Current Limit with 600µs time-out

- IntelliTrip<sup>™</sup> electronic circuit breaker distinguishes between Over-Current and Hard Fault conditions

- Fast shutdown for Hard Faults with a single retry (fault current > 4X current limit value)

- Under voltage threshold hysteresis increased to 135mV

- V<sub>DD</sub> Under-Voltage Lock-Out (UVLO)

- Power Good Control Output

- Monitors both the DRAIN (voltage drop across the FET) and the GATE voltage

- When DRAIN and GATE voltages are within tolerance the Power Good output is latched in the active state

# Applications

- VoIP (Voice over Internet Protocol) Servers

- Telecom systems at -48V

- Negative Power Supply Control

- +24V Wireless Base Station Power

1

## **Related Literature**

- ISL6140/50 Hot Plug Controller, Document # FN9039

- ISL6141/51 Hot Plug Controller, Document # FN9079

- ISL6142/52 Hot Plug Controller, Document # FN9086

- ISL6142/52 EVAL1 Board Set, Document # AN1000

- ISL6116 Hot Plug Controller, Document # FN4778

NOTE: See www.intersil.com/hotplug for more information.

# Pinout

| PWRGD 1           |            | 8 V <sub>DD</sub> |

|-------------------|------------|-------------------|

| OV 2              |            | 7 DRAIN           |

| UV 3              | ISL6140/41 | 6 GATE            |

| V <sub>EE</sub> 4 |            | 5 SENSE           |

ISL6140/41 has active low (L version) PWRGD output pin

ISL6150/51 has active high (H version) PWRGD output pin

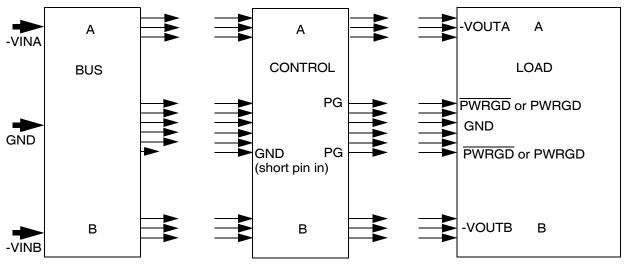

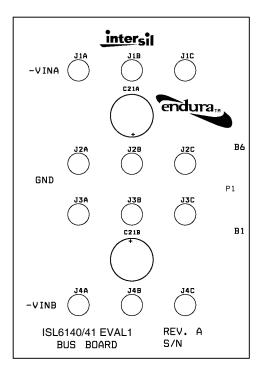

**BUS BOARD**

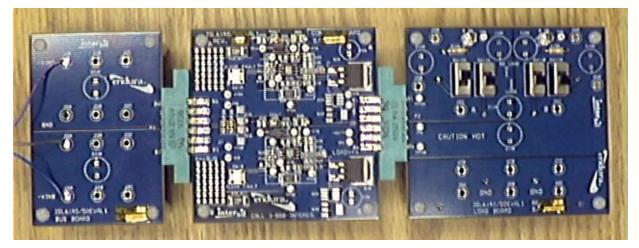

## CONTROL BOARD LOAD BOARD FIGURE 1. THREE BOARD SET PHOTOGRAPH

# Eval Board

- Three-board set with edge connectors to simulate live plug-ins

- Two independent channels, for comparison measurements

- Fully populated; requires only a 48V power supply to start

# Overview

This document assumes the reader is familiar with the hot plug concept, and has a copy of the ISL6140/50, and ISL6141/51datasheets referenced on the first page.

The ISL6140/41EVAL1 Board Set is made up of 3 boards (see Figures 1, 2, and 5 for various representations):

- BUS board: Input -48V power bus

- CONTROL board: IC hot-plug functions

- · LOAD board: Load resistors and capacitors

The 3 board set allows the user to simulate plugging a board into a live edge connector OR simulate plugging a live load into a motherboard.

Most component values have been optimized for performance at -48V; some components need to be changed at either voltage extreme for optimal (or even acceptable) performance. For example, LED brightness is determined by the supply voltage through a current limiting resistor; the brightness at -10V is low, and high at -80V. If the board is to be used at a single fixed voltage level, some components might be changed to accommodate.

- There are two identical channels (A and B); they can share one power supply (connect -VINA and -VINB together, either on the board, or externally), or they can each have their own supply (even at different voltages); there is no interaction between them (other than sharing the common GND). No special power up or down sequencing is required. The default board is shipped with an ISL6140 in Channel A, and an ISL6141 in Channel B. See Figure 7 for schematic. ISL6150 and ISL6151 devices are also supplied with the evaluation kit.

- The boards are labeled for negative supply operation; GND is the most positive voltage, and -VINA and -VINB are the most negative voltages. Note that GND is common for both channels on all three boards. Since most IC signals are referenced to the negative rail, the user may want to reference the voltmeter and oscilloscope GNDs to the negative supply. However, be careful of earth GND

connections (on power supplies or oscilloscopes) that don't match the user's GND.

- The boards can be used in a positive supply configuration, as long as the user renames (mentally or physically) the signals (the GND will become the positive supply, and -VINA and -VINB will become the new GND). Here, both supplies must be the same voltage.

- Boards are set for 54V max operation (using Over-Voltage shutdown) to protect the load resistors. Users have the option to change components and substitute alternate loads. UV is set at 37V.

- Typical load is a -48V to 5V brick regulator.

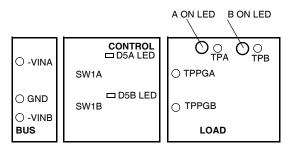

FIGURE 2. LEDs AND TEST POINTS

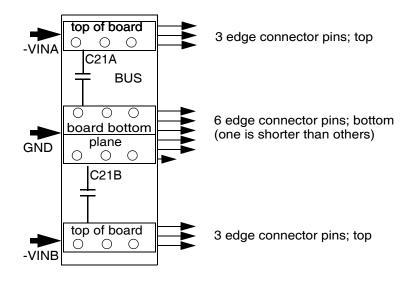

# BUS board (Input -48V Power; Fig. 6)

- Multiple large holes for soldering wires, posts, pins, etc. for input power (-48V and GND typical)

- · Holes for optional input caps

- Edge connector pins plug into Control board

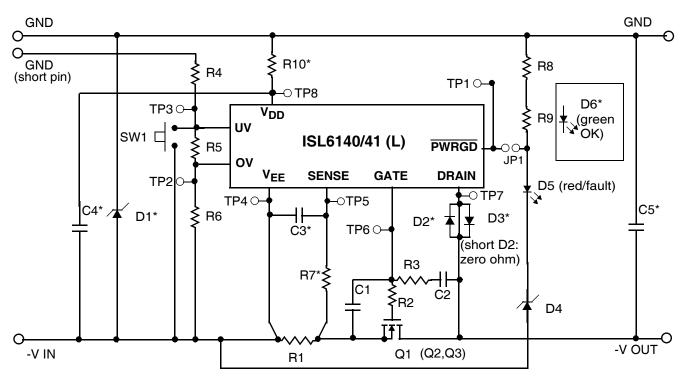

# CONTROL Board (IC Hot-Plug; Fig. 7)

- 2 Identical hot plug channels

- Compare Intersil ISL6140 (L) to ISL6141 (L), or replace the units with the ISL6150/51 and evaluate the active high power good output function.

- Change components for alternate applications

- Red "FAULT" LED (Power Good; for ISL6140/41 only); jumper to disconnect it (if it interferes with logic level)

- Push-button Switch for Over-Current latch reset

- · Footprints for 3 FET outlines; D2PAK, SO-8, SOT-223

- Short pin connection for UV lockout

- Test point for each IC pin

- Small bread-board area for adding user circuitry

- Approximate minimum board area highlighted

- Board application options (See "Optional Components" section)

- Plated through holes for adding load capacitors

- Footprints for RC filter on VDD

- Footprints for RC delay on Over-Current shutdown (applicable for ISL6140/50)

З

- Footprint for DRAIN protection diodes

- Footprint for Over-Voltage clamping suppressor

- Green LED for Power Good OK (ISL6140/41 only)

- Alternate Sense Resistor (0.02Ω) included

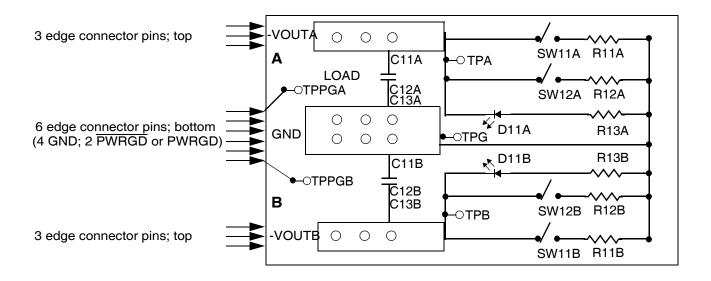

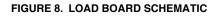

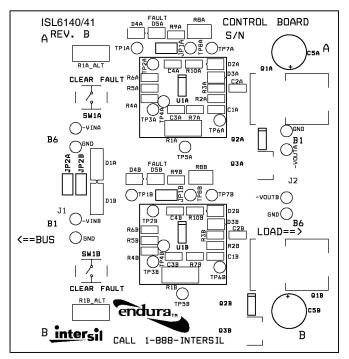

# LOAD Board (R and C Loads; Fig 8)

- Edge connector pins plug into Control board

- Typical Load current is <100mA (limited by power dissipation of the load resistors); Over-Current trip is ~185mA.

- Two load resistors for each channel; one ~80mA, 2nd ~160mA; in parallel ~240mA (Over-Current).

- · Switches to connect the loads in and out

- Multiple holes for soldering wires, pins, posts, for external output load connections (brick regulators are too big and varied to include on the board).

- Holes for optional load caps

- Power Good signal from each channel brought over through edge connector, for use with brick regulator; available on test pins.

- LED Channel "ON" indication

# -48V Hook-Up Instructions

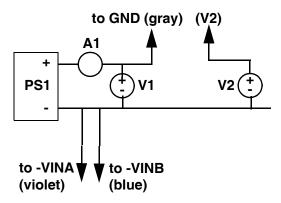

Get one (or two) -48V power supplies (~0.25A current needed per channel; 0.5A total). A positive supply can also be used as long as the user keeps the polarities correct. The two channels can share one voltage supply, can each have their own supply, or can even have two different voltages (no special power-up sequence is needed). If only one channel is being tested, the other can be left unconnected. The following instructions are the same for both channels. As shown in Fig. 3, A1 is an optional ammeter to measure current; V1 is an Voltmeter to measure power supply voltage, and V2 is a voltmeter to look at other signals. Note that the voltmeters are referenced to the negative supply rail.

#### FIGURE 3. HOOK UP

NOTE: If the user substitutes higher current external loads, the power supply capability would need to be increased accordingly.

- 2. All Power off.

- 3. Connect the gray wire to GND (or most positive voltage); connect the -VINA (violet) and -VINB (blue) wire(s) to the negative 48V supply (or the most negative voltage).

- 4. Plug the 3 boards together; from left to right, should be BUS, CONTROL, and LOAD (those labels should be upright, facing the user). Set the switches on the LOAD board to the "No Load" position.

- Turn on supplies to -48V. The FETs should turn on, switching the -VIN voltages to -VOUT; the A ON and B ON LED(s) on the LOAD board should be on. Power supply current (if monitored) should be approximately 8mA.

- 6. A simple check for UV (Under-Voltage) and OV (Over-Voltage) can be done with a variable power supply. From the -48V normal start, increase the voltage to >-54V; the FETs and "ON" LEDs should turn off, until the voltage is lowered (There should be about one volt of hysteresis). Similarly, bring the voltage to <-37V to turn off the FETs and LEDs; again, there is some hysteresis to turn them back on. The ISL6141/51 should have about 4 volts of hysteresis. The ISL40/50 should have about 1V of hysteresis.</p>

NOTE: The Fault LED is not compatible with the ISL6150/51; it will always be on as long as the input power supply is on. The jumper should be disconnected if the ISL6150 or ISL6151 is being evaluated. In addition, one of the loads may need to be switched on for the "ON" LEDs to respond properly to OV or UV.

- 7. Switch on Loads: At 48V, SW11 by itself should give ~80mA of current; SW12 by itself should give ~160mA of current. Both together should give ~240mA, which will exceed the preset Over-Current level ( $0.05V/0.27\Omega = 185$  mA). The FET should turn off, the A/B ON LED should go off, the Fault LED should turn on. Use a scope to monitor the GATE response for the Over-Current shutdown. The ISL6140/50 will turn off the FET immediately (~2uS). The ISL6141/51 will pull the GATE down to ~4V and regulate the current for approximately 600uS before turning off the FET. To return to normal operation, un-switch one or both load resistors, and press and release SW1 (which pulls down on the UV pin, to reset the internal fault latch).

- Disconnect the BUS board from the CONTROL/LOAD; now plug it back in; this simulates a hot plug board being inserted into a live connector. The FETs should turn on in a controlled manner, based on the gate timing components.

- Disconnect the BUS/CONTROL from the LOAD; now plug it back in; this simulates a load being plugged into a powered hot plug on the motherboard.

#### Other Notes:

Current Monitoring: There are several ways to monitor load currents. A voltmeter can be placed across the R1 sense resistor, to calculate the current (I = V/R; R = 0.27 ohms).

For more for detailed measurements, a current probe connected to an oscilloscope can be used. First, place all of the load switches in the "No Load" position. Add a wire loop between -VOUTA (or -VOUTB) to an external load and then back to GND. The load resistors can also be used; just connect the wire loop from -VOUT to one of the load resistor's terminals closest to the switch. Now the load current will flow through the wire loop, and can be monitored. Note that the LED current (~1mA) will not be included in the current loop; but if it interferes with a "zero" current condition, then just un-solder the R13 resistor, in order to disconnect it.

Alternate sense resistor: The R1 sense resistor on the board is 0.27 ohm; this sets the Over-Current shutdown at 185mA. This was done primarily to allow reasonably sized load resistors to be used for initial demonstrations. However, the IC and the boards are certainly capable of switching much higher currents, as long as the user supplies his own external load (the Q1 IRF530 FET, for example, is rated up to 17A). Therefore, an R1\_alt of  $0.02\Omega$  is also supplied on the board for each channel. Un-solder R1 and solder R1\_alt in its place. This will set the Over-Current shutdown at I =  $V/R = 50mV/0.02\Omega = 2.5$  Amps. Similarly, the user can supply his own alternate value to set the trip point wherever he wants to. Keep in mind that the power supply must also be rated to handle the higher load current.

Over-Voltage is set to 54V to protect the load resistors; the R4,R5,R6 values can be changed for other loads. A more typical value for OV is around 71V, the high end of the range for a 48V supply application. See the ISL6140 and ISL6141 data sheets for more details on how to select the resistors.

There are many test pins that can be used for meter or oscilloscope probes. Discrete components might even be soldered to them, if necessary. See the various "Board Labels" section.

Additional or alternative loads can be externally connected to the LOAD board.

Individual components can be un-soldered and replaced with alternative values, if desired.

There are many optional components that can be soldered in, as desired (see "Optional Components" section).

Be sure the external components are properly rated for the application voltage; this is especially true for input or output capacitors, for example; they should be rated for 100V, if the full voltage range will be used.

The fault LED is intended for display purposes; the implementation used is not necessarily a satisfactory solution for a production design. Aside from being useful only with the ISL6140/41, the brightness varies greatly with the supply voltage. If the signal is to be used as a logic output, as well as drive an LED, then the voltage level must also be compatible with the signal it drives (the jumper JP1 disconnects the LED from the pin, to separate the functions). The present circuit also clamps the output voltage; a 3V zener diode was included to make the clamp voltage around 4.5V, compatible with most logic levels. Finally, the LED

provides a current path between the PWRGD pin back to the VEE pin, when the FET is off; this may not be desirable in the system (referencing the LED to the DRAIN pin doesn't work, since under most faults, when the FET turns off, the DRAIN will then be floating.

Since the ISL6140/41 PWRGD output is an open-drain, pulldown device, an LED connected to the positive supply is another option. But since the LED will be on during normal operation, and off during a fault, a green "OK" LED is suggested. See "Optional Components" section for more details.

# **Required Components** (Same for both A and B channels; See Fig. 4 and 7)

U1 is the ISL6140 (L) or ISL6141 (L) Intersil hot plug controller IC. The ISL6141 is an enhanced version of the ISL6140 and is pin for pin compatible. The functional differences are summarized on page 1.The ISL6150 and ISL6151 function and perform the same as the ISL6140 and ISL6141 respectively, with the exception of their power good outputs which are active high.

R4, R5, R6, are the resistors that divide the input power supply voltage down to the Over-Voltage (OV) and Undervoltage (UV) trip points. The top of the resistor divider is connected to the short-pin GND.

R3, C2, R2, C1 control the inrush current, prevent momentary turn-on during power-up, and keep the gate pin from oscillating. See ISL6140/41 data sheets for more details.

R1 is the Over-Current sense resistor.  $I_{OC}$  = 50 mV / R1.

Q1 is the FET that switches the voltage from the input BUS to the LOAD. It uses a D2PAK package.

R8, R9, D4, D5 create the red LED "FAULT" indication for the ISL6140/41 (L version). R8 sets the LED current; R9 is just a zero ohm placeholder; D5 is the LED, and D4 is a 3V zener. Note that when the PWRGD open-drain pull-down output turns on (Power is Good), the fault LED is off. When the output turns off, the fault LED will turn on; the voltage would rise to a high value, but the zener and LED will clamp it to approximately 4.5V.

| TABLE 1. NEEDS A DESCRIPTION |                                           |  |  |

|------------------------------|-------------------------------------------|--|--|

| R1 = 0.02Ω (1%)              | C1 = 150nF (25V)                          |  |  |

| R2 = 10Ω (5%)                | C2 = 3.3nF (100V)                         |  |  |

| $R3 = 18k\Omega$ (5%)        | Q1 = IRF530 (100V, 17A, 0.11 $\Omega$ )   |  |  |

| R4 = 562kΩ (1%)              | $CL = 100 \mu F (100V)$                   |  |  |

| R5 = 9.09kΩ (1%)             | RL = equivalent resistance of the<br>Load |  |  |

| R6 = 10kΩ (1%)               |                                           |  |  |

# **Optional Components** (Same for both A and B channels; See Fig. 7)

R10 and C4 make an RC filter for the VDD pin. It is used to isolate some kinds of system supply noise from the IC. For example, it may help filter out glitches that could trigger OV or UV (which shut off the FET) if near their trip points.

D1 is a voltage suppressor, which can help protect the board components from transient voltages that exceed the normal operating range allowed (absolute maximum is 100V).

D2 and D3 may be used to block inductive transients that might pull the drain pin negative with respect to the VEE pin. The ISL6140/41 (L version) uses one diode (D2); the ISL6150/51 (H version) uses both diodes. The diodes have a second effect of offsetting the drain trip points for the PWRGD/ PWRGD output. The default board has one of the diodes shorted out with zero ohms; that should be removed before adding one or two diodes.

R7 and C3 make an RC time constant to lengthen the time allowed in the Over-Current condition for the ISL6140, before shutting down. Without them, any pulse longer than the 2–4 usec spec would latch off the output. If noise pulses wider than that are expected (and won't cause other damage), then set the filter to a time longer than those pulses. Note, however, that the FET must be able to safely handle the current and power dissipation for that longer time period. The default boards are shipped with R7 = zero ohms.The ISL6141/51 does not require these components, as the device has a fixed 600uS time-out and programmable current limiting.

Q2 and Q3 are alternate package options for Q1 FETs. Q2 is an 8-pin SOIC, using a standard pinout (S=1, 2, 3, G=4, D=5-8). Q3 is an SOT-223 package. Since all three pins of all three packages are wired in parallel, with no jumpers, it is recommended that only one of the 3 be populated at any given time.

R1\_alt is a 0.020  $\Omega$  sense resistor; if used instead of R1 (unsolder R1, and solder in R1\_alt) it will produce an Over-Current trip point of (50mV /0.020 $\Omega$ ) = 2.5 Amps. CAUTION: The load resistors supplied with the LOAD board combined only give about 0.25Amps for each channel; an additional external load or shorting mechanism will then be needed to trip the Over-Current.

C5 is a load capacitor that can be placed on the CONTROL board (in addition to the three cap footprints on the LOAD board). It can be any value consistent with the application. Note the polarity for electrolytic capacitors.

D6 is a green LED that can be used as a PWRGD "OK" indicator, instead of a red "FAULT" LED. It should only be used with the ISL6140/41. R8 sets the LED current; D6 LED replaces R9, and D4 and D5 are disconnected (remove either one to open circuit).

# BUS Board Labels (See Fig. 11)

- -VINA = J1A, J1B, J1C

- GND = J2A, J2B, J2C

- GND = J3A, J3B, J3C

- -VINB = J4A, J4B, J4C

- C21A = optional input capacitor for -VINA (to GND)

- C21B = optional input capacitor for -VINB (to GND)

Edge Connector Pins P1;

- Top pins B6, B5, B4 = -VINA

- Top pins B3, B2, B1 = -VINB

- Bottom pins A6 A1 = GND

- Note that pin A3 is shorter than the others. This pin is thus expected to be the last one to make contact; it is used to hold the IC's in reset until all pins are have made good contact).

# CONTROL Board Labels (See Fig. 10)

#### Edge Connector Jack J1

- Top pins B6, B5, B4 = -VINA

- Top pins B3, B2, B1 = -VINB

- Bottom pins A6, A5, A4, A2, A1 = GND

- Bottom pin A3 = SHORT GND (last pin to make contact; connected to the UV/OV resistor divider on both channels)

- JP2A and JP2B are optional jumpers (not populated); if the SHORT GND function is not desired, connecting the two pins on either jumper will effectively eliminate the

shorter pin (the UV/OV resistor divider will be connected to the longer GND pins).

#### Edge Connector Jack J2

- Top pins B6, B5, B4 = -VOUTB

- Top pins B3, B2, B1 = -VOUTA

- Bottom pins A5, A4, A3, A2, = GND

- Bottom pins A1 = PWRGDA; A6 = PWRGDB (these signals are brought over to the LOAD board, in the event the user needs them (for example, to enable a brick regulator). There is a also test point for each (TPPGA, TPPGB) on the LOAD board.

#### Test Pins

- -VINA, GND, -VINB, GND (from J1)

- TP1A TP8A (each IC pin number has its own TP)

- TP1B TP8B (each IC pin number has its own TP)

- -VOUTA, GND, -VOUTB, GND (from J2)

#### Switches

- SW1A = momentary depress the push button to bring Channel A UV (IC pin 3) to VEE, in order to clear Over-Current fault latch.

- SW1B = same as above for Channel B

#### Jumpers

- JP1A = shorting the two pins together connects the Channel A PWRGD signal (IC pin 1) to the red fault LED indicator. This jumper should be removed for the ISL6150/51 (H version), because the LED circuit is not valid (the LED would remain on for either state). It should also be removed if the LED circuit interferes with the logic levels needed externally (such as for a brick regulator; the present board clamps to ~4.5V when the LED is on). Note that this circuit may not be the most efficient or costeffective; it is just meant to be functional for the Eval board.

- JP1B = same as above for Channel B

#### LEDs

- D5A = red "FAULT" LED; it comes on if the PWRGD pin on the ISL6140/41 goes high; it represents some kind of fault, usually a shorted output or an Over-Current shutdown. it will also turn on if the FET is turned off for OV, UV or UVLO fault conditions.

- D5B = same as above for Channel B.

# LOAD Board Labels (See Fig. 9)

## CAUTION HOT

The load resistors are mounted on the bottom of the LOAD board, but the heat can be felt through the top of the board. Be careful how you handle the board, especially while gripping it for plugging or unplugging.

#### Edge Connector Pins P2;

- Top pins B6, B5, B4 = -VOUTB

- Top pins B3, B2, B1 = -VOUTA

- Bottom pins A5, A4, A3, A2 = GND

- Bottom pins  $A1 = \overline{PWRGD}A$ ;  $A6 = \overline{PWRGD}B$

## Test Pins

- TPPGA (J1, pin A1); PWRGDA

- TPPGB (J1, pin A6); PWRGDB

- TPG (J1, pin A5 A2); GND

- TPA (also J5A, J5B, J5C); -VOUTA

- TPB (also J6A, J6B, J6C); -VOUTB

- J7A, J7B, J7C, J8A, J8B, J8C; GND

# **Optional Capacitors**

- C11A, C12A, C13A; for -VOUTA

- C11B, C12B, C13B; for -VOUTB

#### Switches (note the Load and No Load positions)

- SW11A switches in/out a 330  $\Omega$  load R11A for -VOUTA

- + SW12A switches in/out a  $620\Omega$  load R12A for -VOUTA

- Both Switches together will create an Over-Current shutdown for Channel A (with R1 = 0.27Ω)

- + SW11B switches in/out a 330 $\Omega$  load R11B for -VOUTB

- SW12B switches in/out a  $620\Omega$  load R12B for -VOUTB

- Both Switches together should create an Over-Current shutdown for Channel B (with R1 = 0.27 ohms)

#### LEDs

- D11A is on when -VOUTA is switched on (through the Q1A FET). Note it is independent of whether either of the load resistors is connected.

- Same as above for Channel B (Note that D11B was not labeled on the board; look for "B ON").

ISL6140/41 EVAL boards (BUS Input, CONTROL, LOAD Output)

FIGURE 5. THREE BOARD SET

ISL6140/41 EVAL boards BUS (Input)

FIGURE 6. BUS BOARD SCHEMATIC

ISL6140/41 EVAL board (CONTROL) (Two identical channels (A/B) on board; all components have a suffix A or B).

ISL6140/41 EVAL boards LOAD (Output)

# Bill Of Material

#### TABLE 2. BILL OF MATERIAL

| Component  | Name                               | Size              | Description                                       |

|------------|------------------------------------|-------------------|---------------------------------------------------|

|            | CONTROL BOARD BOM                  |                   |                                                   |

| U1 A/B     | ISL6140 (A); ISL6141 (B)           | 8-SOIC            |                                                   |

| Q1 A/B     | IRF530 or equivalent               | SMD-220(D2PAK)    |                                                   |

| Q2 A/B     | Optional FET                       | 8-SOIC            | DNP;                                              |

| Q3 A/B     | Optional FET                       | SOT-223           | DNP;                                              |

| R1 A/B     | Current Sense Resistor             | 2512, 0.27ohm,5%  | 1W                                                |

| R1_alt A/B | Current Sense Resistor (alternate) | 2512, 20mohm,1%   | 1W                                                |

| R2 A/B     | Gate Resistor                      | 0805,10 ohm,5%    |                                                   |

| R3 A/B     | Power up Resistor                  | 0805,18k ohm,5%   |                                                   |

| R4 A/B     | UV/OV resistor divider             | 0805,562k ohm,1%  |                                                   |

| R5 A/B     | UV/OV resistor divider             | 0805,5.9k ohm,1%  |                                                   |

| R6 A/B     | UV/OV resistor divider             | 0805,13.3k ohm,1% |                                                   |

| R7 A/B     | (Placeholder); OC time stretch     | 0805,0 ohm,5%     | optional RC stretch for ISL6140/50 only (with C3) |

| R8 A/B     | LED current Resistor               | 1210,39k ohm,5%   | 1/4W                                              |

| R9 A/B     | (Placeholder);                     | 0805,0 ohm,5%     | optional green "OK" LED                           |

| R10 A/B    | (Placeholder); RC filter for VDD   | 0805,0 ohm,5%     | optional RC filter (with C4)                      |

| C1 A/B     | Power up Capacitor                 | 0805,150nF,25V    |                                                   |

| C2 A/B     | Feedback Capacitor                 | 0805,3.3nF,100V   |                                                   |

| C3 A/B     | Optional RC                        | 0805              | DNP (with R7)                                     |

| C4 A/B     | Optional RC filter for VDD         | 0805,0.1uF,100V   | DNP                                               |

| C5 A/B     | Optional Load Capacitor            | electrolytic      | DNP; Through-hole;                                |

| D1 A/B     | SMAT70A                            | SMA               | Voltage suppressor                                |

| D2,D3 A/B  | 1N4148                             | SOD-123; 75V      | Blocking diode                                    |

| D4 A/B     | 3V zener diode                     | S-mini 2P         |                                                   |

| D5 A/B     | Red LED                            | 0805              |                                                   |

| D6 A/B     | Green LED                          | 0805              | DNP; optional                                     |

| SW1 A/B    | UV reset push button;              |                   | Normally Open                                     |

| JP1 A/B    | Two Pin Jumper; shorting shunt     |                   | Isolate PWRGD, LED                                |

|            | BUS BOARD BOM                      |                   |                                                   |

| C21 A/B    | Optional Input Capacitor           | electrolytic      | DNP: through-hole;                                |

|            | LOAD BOARD BOM                     |                   |                                                   |

| R11 A/B    | Load Resistor                      | 620 ohm,5%,5W     | through-hole;                                     |

| R12 A/B    | Over-Load Resistor                 | 330 ohm,5%,10W    | through-hole;                                     |

| R13 A/B    | LED Current Resistor               | 39 kohm, 5%, 1/4W | through-hole;                                     |

## TABLE 2. BILL OF MATERIAL (Continued)

| Component                     | Name                                                           | Size         | Description        |

|-------------------------------|----------------------------------------------------------------|--------------|--------------------|

| D11 A/B                       | Red LED                                                        | T1-3/4       | through-hole;      |

| SW11 A/B<br>SW12 A/B          | Load Slide Switch                                              |              | through-hole;      |

| C11 A/B<br>C12 A/B<br>C13 A/B | Optional Load Capacitors                                       | electrolytic | DNP; through-hole; |

|                               |                                                                |              |                    |

|                               | Note: Surface Mount Resistors are 1/10W unless otherwise noted |              |                    |

|                               | Note: DNP = Do Not Populate                                    |              |                    |

# **Component Placement and Labels**

NOTE: D11B NOT LABELED

FIGURE 9. LOAD BOARD

FIGURE 10. CONTROL BOARD

## **Component Placement and Labels**

FIGURE 11. BUS BOARD

All Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com